История развития RISC-V

Работы над стандартом

В январе 2015 года была проведена первая профильная конференция для разработчиков

В том же 2015 году был создан консорциум

В 2018 году консорциум

В марте 2020 года новая штаб-квартира консорциума

Архитектура RISC-V

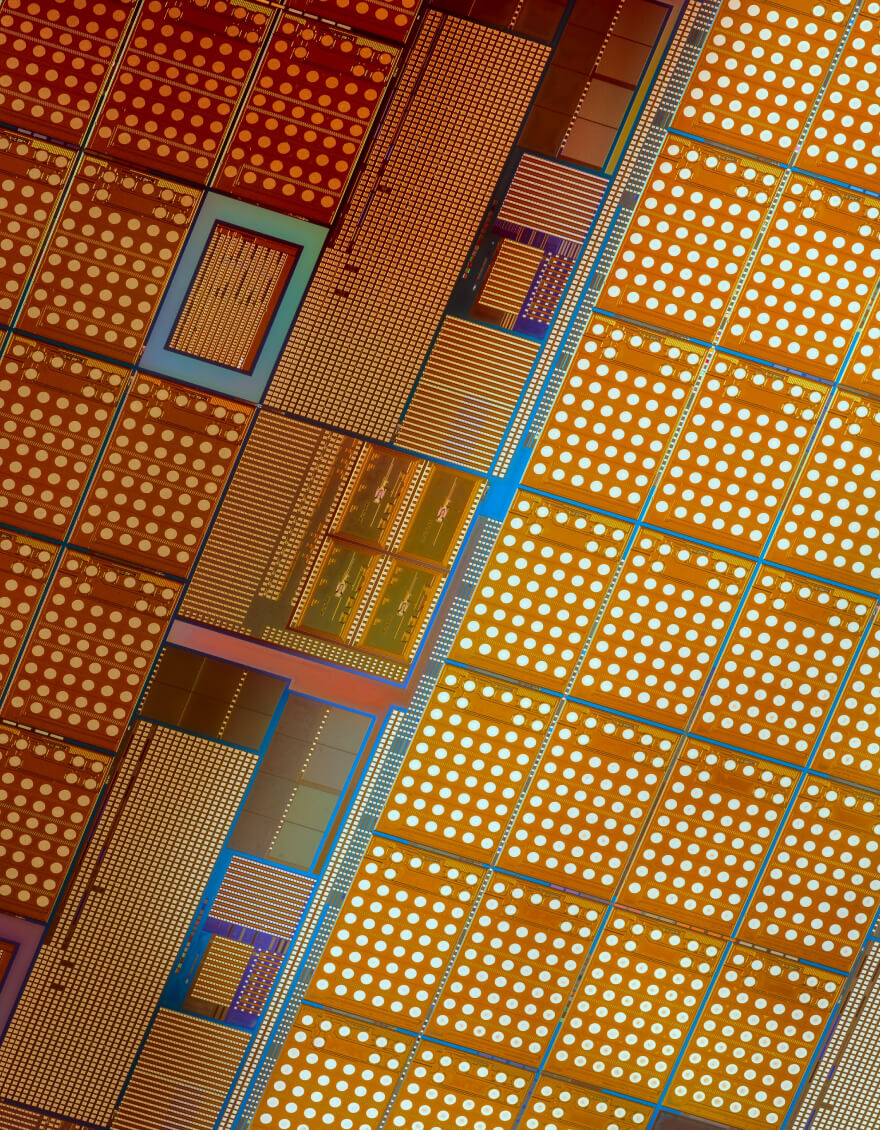

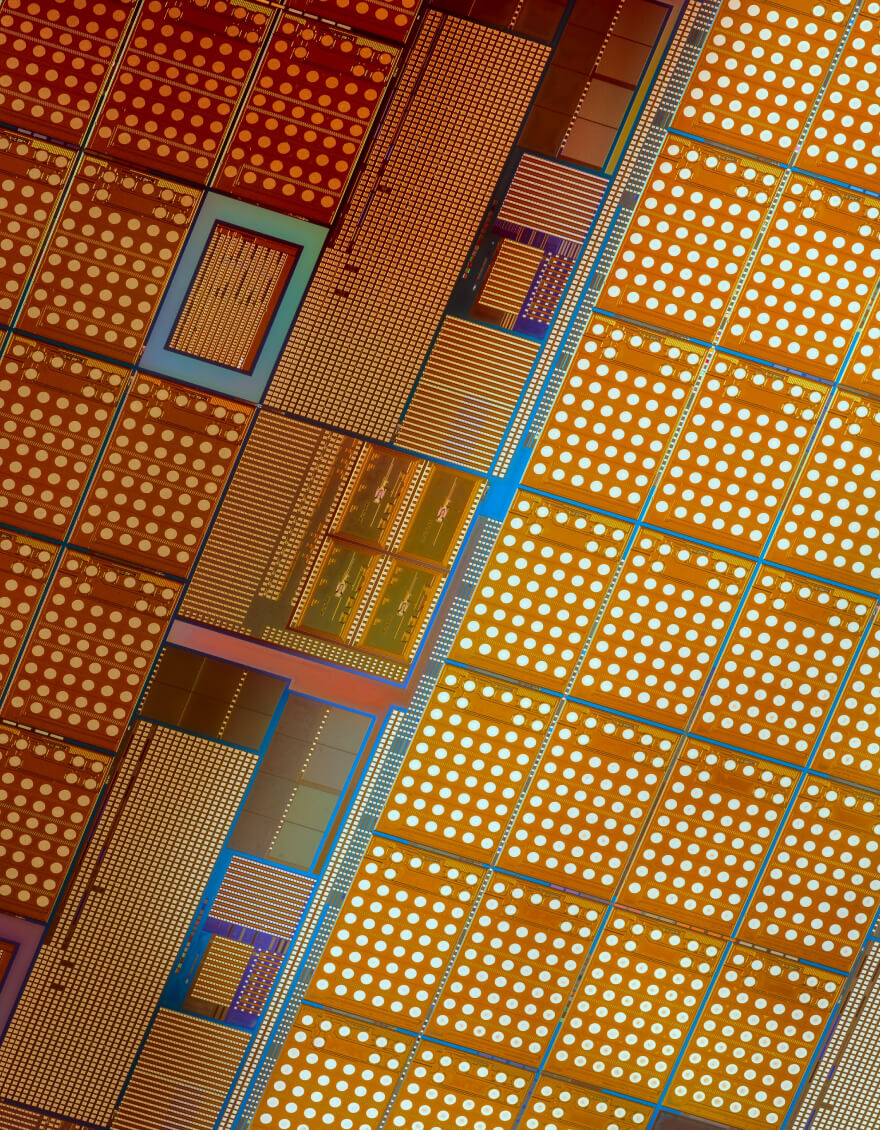

Благодаря открытости архитектуры разработчики совместимых процессоров могут создавать собственные высокопроизводительные версии и реализовывать эффективные варианты архитектур, оптимизированных для конкретных задач. Например, варьировать длину конвейера, размер и организацию кэша данных и команд и многое другое.

Открытость архитектуры позволяет производителям проектировать специализированные процессоры для различных областей: от устройств интернета вещей до систем искусственного интеллекта и высоконагруженных серверов общего назначения.

Свободная лицензия

Интерес к

Устав консорциума

Основные цели консорциума — развитие и продвижение стандарта

Международное комьюнити

Многочисленное международное сообщество стремительно развивает архитектуру: ратифицируются новые спецификации, создаются комитеты по развитию технологий, расширяется программная экосистема. Решения на

Расположение штаб-квартиры консорциума

В середине 2022 года число участников сообщества составило более 3000 резидентов из 70+ стран, включая большую часть мировых технологических лидеров: Intel, Google, IBM, Nvidia, Western Digital, Huawei, Qualcomm, Renesas, NXP и многих других.